Faculty of Engineering Benha university Electrical Eng.Dept. Dr Hossam Labib Zayed

Design of Electronic Circuits(E401) Final-Term Exam Date: 28/5/2016 Time: 3 Hours

### Answer all the following questions:

- Q1: Design a BJT differential amplifier that provides two single-ended outputs. The amplifier is to have a differential gain of at least 100 V/V, a differential input resistance  $\geq 10 \text{ k}\Omega$ , and a common mode gain no greater than 0.1 V/V. Use a 2-mA current source for biasing. Give the complete circuit with component values and suitable power supplies that allow for  $\pm 2$  V swing at each collector. The BJTs available have  $\beta \geq 100$ .

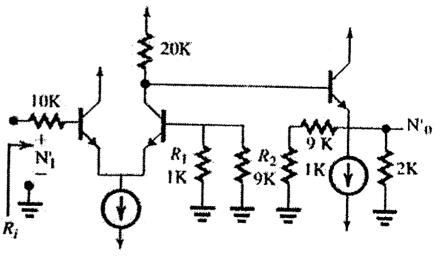

- Q2:The 4-stages direct coupled op-amp circuit shown in Fig.(1) is operating at room temperature. Assuming all transistors have  $\beta = 200$ .

- a) Perform an approximate dc analysis to calculate the current and voltage everywhere in the circuit (assuming  $|V_{BE}|=0.7v$ , neglect the Early effect). Note that Q<sub>6</sub> has four times the area of each of Q<sub>9</sub> and Q<sub>3</sub>.

- b) Compute the differential input resistant.

- c) Compute the overall voltage gain of the multistage amplifier. What is the input offset voltage if  $R_1$  changed by 2%

- Q3: For the current mirror shown in Fig.(2), derive an expression for the current transfer function  $I_o(s)/I_i(s)$  as a function of transistor parameters taking into account the BJT internal capacitances and neglecting  $r_x$  and  $r_o$ . Assume the BJTs to be identical.

- Q4: Consider the complementary BJT class B output stage and neglect the effects of finite  $V_{BE}$  and  $V_{CEsat}$ . For  $\pm 10V$  power supplies and a 100 $\Omega$  load resistance,

- a) What is the maximum sine wave output power available?

- b) What is the power-conversion efficiency?

- c) Show how to reduce the zero-crossing distortion in class B power amplifier?

- Q5: The circuit shown in Fig.(3) consists of a differential stage followed by an emitter follower, with series-shunt feedback supplied by the resistors  $R_1$  and  $R_2$ . Assuming that the dc component of  $V_s$  is zero, and that  $\beta$  of the BJTs is very high, find:

- a) The dc operating current of each of the three transistors and show that the dc voltage at the output is approximately zero.

- b) The open loop gain (A).

- c) The feedback gain (*B*).

- d) The input resistance  $R_{in}$ , and The output resistance  $R_{out}$ . Assume that the transistors have  $\beta = 100$ .

Q1: Design a BJT differential amplifier that provides two single-ended outputs. The amplifier is to have a differential gain of at least 100 V/V, a differential input resistance  $\geq 10 \text{ k}\Omega$ , and a common mode gain no greater than 0.1 V/V. Use a 2- mA current source for biasing. Give the complete circuit with component values and suitable power supplies that allow for  $\pm 2$  V swing at each collector. The BJTs available have  $\beta \geq 100$ .

Solution:

From DC

$$2 I_E = I \implies I_E = I_2$$

$V_e = \frac{4T}{I_E} = \frac{25mV}{MA} = 25\Omega$

$V_e = \frac{25mV}{MA} = 25\Omega$

$V_e = \frac{25mV}{MA} = 25\Omega$

$V_e = 25m \implies There is must be  $F_E$  in the differential

$AnpLifter To mat The design requirement of Rid > 10KR$

$V_e = 2(1+B)(V_e + R_E)$

$V_e = 2(1+B)(V_e + R_E)$

$V_e = 2(1+100)(25 + R_E)$

$F_E = \frac{10K}{2 \times 101} - 25 = 25\Omega$

$-For differential cain Ad = 100 VIV and two single ended

$OIP \implies Ad = \frac{V_O}{V_I} = \frac{V_O}{V_I} = \frac{Total Vesistance at Callector}{Total (Resistance at Callector)}$

$Ad = \frac{K_C}{2(E_F + 2)E} = \frac{R_C}{2(E_F + E_E)} = 100$

$V_e = \frac{R_C}{2(25 + 25)} \implies R_C = 10 KR$

$V_e = V_{CC} - ICR_C \implies V_{CC} = V_C + ICR_C = 2 + IM XIOIT$

$V_{CC} = 12N'$  Then  $A_{CC} = \pm 12N$$$

(1

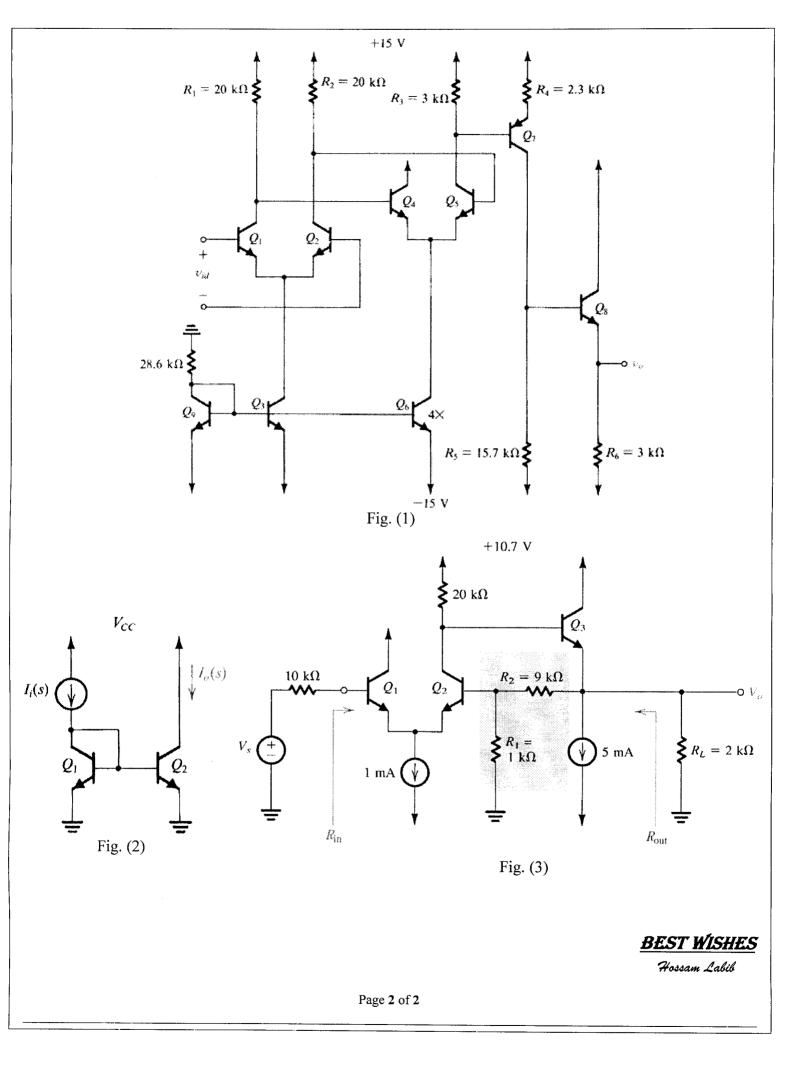

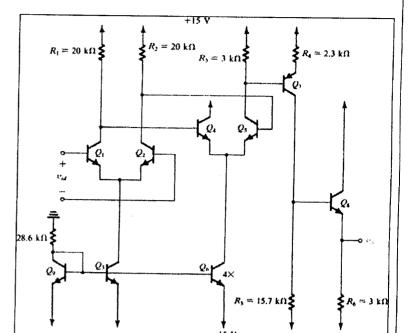

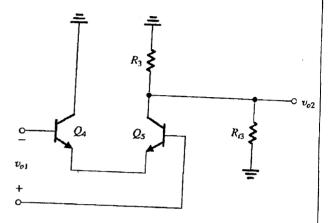

#### The 4-stages direct coupled op-amp circuit shown in Fig.1 is operating at room temperature. Assuming all transistors have $\beta = 200$

- a) Perform an approximate dc analysis to calculate the current and voltage everywhere in the circuit (assuming  $|V_{BE}|=0.7v$ , neglect the Early effect). Note that Q<sub>6</sub> has four times the area of each of  $Q_9$  and  $Q_3$ .

- b) Compute the differential input resistant.

- c) Compute the overall voltage gain of the multistage amplifier.

- $Q_3$ Qu  $R_{\rm s} = 15.7 \, {\rm k}\Omega$ d) What is the input offset voltage if  $R_1$  changed by 2%

#### Solution:

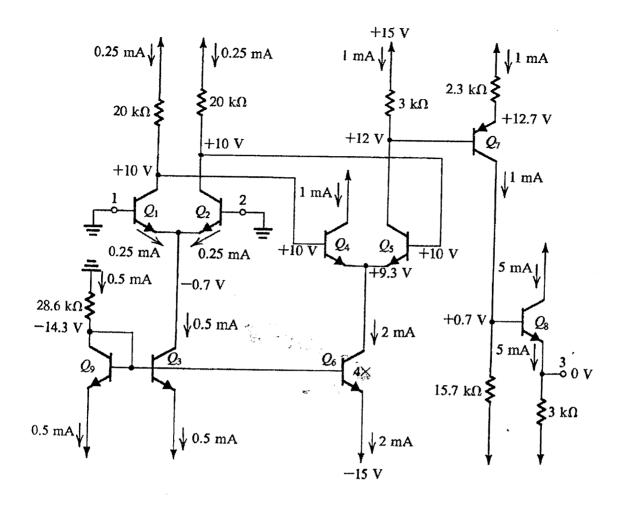

(a) The values of all dc currents and voltages are indicated on the circuit diagram. These values were calculated by ignoring the base current of every transistor-that is, by assuming  $\beta$  to be very high. The analysis starts by determining the current through the diode-connected transistor Q<sub>9</sub> to be 0.5 mA. Then we see that transistor Q<sub>3</sub> conducts 0.5 mA and transistor Q<sub>6</sub> conducts 2mA. The current-source transistor  $Q_3$  feeds the differential pair ( $Q_1$ ,  $Q_2$ ) with 0.5 mA. Thus each of  $Q_1$  and  $Q_2$  will be biased at 0.25 mA. The collectors of  $Q_1$ and  $Q_2$  will be at [+15 - 0.25 x 20] =+10 V.

Proceeding to the second differential stage formed by Q4 and Q5, we find the voltage at their emitters to be [+10 - 0.7] = 9.3 V. This differential pair is biased by the current-source transistor  $Q_6$ , which supplies a current of 2 mA; thus  $Q_4$ andQ5 will each be biased at 1 mA. We can now calculate the voltage at the collector of Q<sub>5</sub> as  $[+15 - 1 \times 3] = +12$  V. This will cause the voltage at the emitter of the pnp transistor  $Q_7$  to be + 12. 7 V, and the emitter current of  $Q_7$ will be (+15 - 12.7)/2.3 = 1 mA. The collector current of Q<sub>7</sub>, 1 mA, causes the voltage at the collector to be  $[-15 + 1 \times 15.7] = +0.7$  V. The emitter of Q<sub>8</sub> will be 0.7 V below the base; thus output terminal 3 will be at 0 V.

Finally, the emitter current of Q8 can be calculated to be [0 - (-15)]/3 = 5 mA.

2

$Q_2$ :

(b)The input differential resistance  $R_{id}$  is given by: Rid =  $r_{\pi 1} + r_{\pi 2}$

Since  $Q_1$  and  $Q_2$  are each operating at an emitter current of 0.25 mA, it follows that  $r_{e1}=r_{e2}=25/0.25=100\Omega$  for  $\beta = 200$ ; then

$\begin{array}{l} r_{\pi 1} = r_{\pi 2} = 201 \ x \ 100 = 20.1 \ k\Omega \\ Thus \qquad R_{id} = 40.2 k\Omega \end{array}$

(c)To evaluate the gain of the first stage we first find the input resistance of the second stage, R  $_{i2}$ ,

$R_{i2} = r_{\pi 4} + r_{\pi 5}$ Q<sub>4</sub> and Q<sub>5</sub> are each operating at an emitter current of 1mA; thus

$r_{\pi 4} = r_{\pi 5} = 201 \text{ x} 25 = 5.025 \text{ k} \Omega$

$r_{e4} = r_{e5} = 25 \Omega$

$R_{i2} = 10.05 \text{ k}\Omega.$

Thus

$R_{1}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{4$

.

3

This resistance appears between the collectors of Ql and Q2, as shown in - Fig. Thus the gain of the first stage will be

$$A1 \equiv \frac{v_{o1}}{v_{id}} \simeq \frac{\text{Total resistance in collector circuit}}{\text{Total resistance in emitter circuit}} = \frac{R_{i2} \parallel (R_1 + R_2)}{r_{e1} + r_{e2}}$$

$$= \frac{10.05k \parallel 40k}{200} = \frac{8031.97}{200} = 40.16 \ \frac{V}{V}$$

Figure 2 shows an equivalent circuit for calculating the gain of the second stage. As indicated, the input voltage to the second stage is the input voltage of the first stage,  $v_{ol}$ . Also shown is the resistance  $R_{i3}$  which is the input resistance of the third stage formed by  $Q_7$ . The value of  $R_{i3}$  can be found by multiplying the total resistance in the emitter of  $Q_7$  by  $(\beta + 1)$ :

$R_{i3} = (\beta + 1)(R4 + re7)$ Since Q<sub>7</sub> is operating at an emitter current of 1 mA,  $r_{c7} = 25/1 = 25\Omega$

$$R_{i3} = 201 \text{ x} (2.3 \text{ k} + 25) = 467.325 \text{ k}\Omega$$

We can now find the gain A2 of the second stage as the ratio of the total resistance in the collector circuit to the total resistance in the emitter circuit:

$$A2 = \frac{v_{o2}}{v_{o1}} = -\frac{(R_3 \parallel R_{i3})}{r_{e4} + r_{e5}}$$

$$= -\frac{(3k \parallel 467.325k)}{50} = \frac{2980.86}{50} = -59.6 \ V/V$$

To obtain the gain of the third stage we refer to the equivalent circuit shown in Fig., where  $R_{i4}$  is the input resistance of the output stage formed by Q8. Using reflection resistance-reflection rule, we calculate the value of  $R_{i4}$  as

$$R_{i4} = (\beta + 1)(r_{e8} + R_6)$$

where

$$r_{e8} = 25/5 = 5\Omega$$

$R_{i4} = 201(5 + 3000) = 604.005 \text{ k}\Omega$

The gain of the third stage is given by

$$A3 \equiv \frac{v_{o3}}{v_{o2}} = -\frac{(R_5 \parallel R_{i4})}{r_{e7} + R_4} = -\frac{(15.7k \parallel 604.005k)}{25 + 2.3k}$$

$$= -\frac{15.302k}{2.325k} = -6.58 \frac{V}{V}$$

Finally, to obtain the gain A4 of the output stage we refer to the equivalent circuit in Fig. and write

$Q_8$

-0 vo

1/03 Q

$$A4 \equiv \frac{v_o}{v_{o3}} = \frac{R_6}{R_6 + r_{e8}} = \frac{3000}{3000 + 5} = 0.998 \simeq 1$$

The overall voltage gain of the amplifier can then be obtained as follows:

$$\frac{v_o}{v_{id}} = A1A2A3A4 = 40.16 \times -59.6 \times -6.58 \times 1 = 15749.5$$

(d) The input offset voltage if  $R_1$  changed by 2%

The input offset voltage  $V_{OS}$

$$|V_{OS}| = V_T \left(\frac{\Delta R_c}{R_c}\right) = V_T \left(\frac{\Delta R_1}{R_1}\right) = 25m \times 0.02 = 0.5mV$$

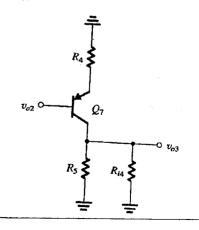

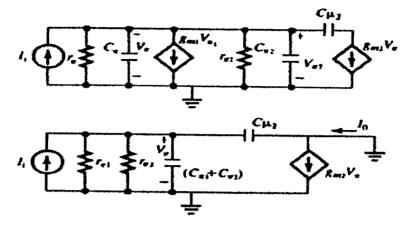

Q3:For the current mirror shown in Fig.(2), derive an expression for the current transfer function  $I_o(s)/I_i(s)$  as a function of transistor parameters taking into account the BJT internal capacitances and neglecting  $r_x$  and  $r_o$ . Assume the BJTs to be identical.

#### Solution:

$$V_{\pi} = \frac{I_{1}}{\left(\frac{1}{r_{e1}} + \frac{1}{r_{\pi 2}}\right) + s(C_{\pi 1} + C_{\pi 2} + C_{\mu 2})}$$

$$I_{o} = g_{\mu 2}V_{\pi} - C_{\mu}sV_{\pi}$$

$$= \frac{(g_{m2} - C_{\mu}s)I_{i}}{\left(\frac{1}{r_{e1}} + \frac{1}{r_{\pi 2}}\right) + s(C_{\pi 1} + C_{\pi 2} + C_{\mu 2})}$$

$$I_{\mu} = g_{m2} - C_{\mu}s$$

$$\frac{1}{I_i} = \frac{C_{\pi_2} - C_{\mu_2}}{\left(\frac{1}{r_{e1}} + \frac{1}{r_{\pi_2}}\right) + s(C_{\pi_1} + C_{\pi_2} + C_{\mu_2})}$$

$$g_{m1} = g_{m2}, C_{m1} = C_{m2}$$

$$\frac{I_0}{I_i} = \frac{g_m - C_{\mu}s}{\left(\frac{1}{r} + \frac{1}{r}\right) + (C_{\mu} + 2C_{\pi})s}$$

$$= \frac{1 - \frac{C_{\mu}}{g_{m}}s}{\left(\frac{1}{g_{m}}r_{e} + \frac{1}{g_{m}}\right) + s\frac{C_{\mu} + 2C_{\mu}}{g_{m}}}$$

$$g_{m}r_{e} = \frac{I_{C}V_{T}}{V_{T}I_{E}} = \alpha = \frac{\beta}{\beta + 1}$$

$$s_r = \beta$$

$$\Rightarrow \frac{I_O}{I_i} = \frac{1 - \frac{C_\mu}{g_m}s}{1 + \frac{1}{\beta} + \frac{1}{\beta} + s(2C_\pi + C_\mu)/g_m}$$

$$\frac{I_O}{I_i} = \frac{1}{1 + \frac{2}{\beta}} \frac{1 - s\frac{C_\mu}{g_m}}{1 + s\frac{(2C_\pi + C_\mu)}{g_m(1 + \frac{2}{\beta})}}$$

$$I_{i}(s) \bigoplus_{Q_{1}} \bigcup_{Q_{2}} \bigcup_{Q_$$

6

# Qu: Consider the complementary BJT class B output stage and neglect the effects of finite $V_{BE}$ and $V_{CEsat}$ . For ±10V power supplies and a 100 $\Omega$ load resistance, a) What is the maximum sine wave output power available? b) What is the power-conversion efficiency? c) Show how to reduce the zero-crossing distortion in class B power amplifier? + Vcc = +10 J Solution a) The average Load power PL = 1/2 No. Q<sub>N</sub> where to is The peak complitude of OIP Sike ware V. - The maximum sine wave ofp power occurs when No = Nec Then Pulmar = 1/2 Nac Pulmar = 1/2 PL 1cc = -10V $=\frac{1}{2}\frac{(10)^2}{100}=0.5W$ (b) The power conversion efficiency 2 = Th where Ps is the total supply Rowan P3 = Ps+ + Ps-: The average power drawn from each of The Two Power Supplies will be The Same - Then $P_{S+} = P_{S-} = \frac{1}{\pi} \frac{V_0}{P_L} Vcc = \frac{1}{\pi} \frac{(1_0)}{1_{T-}} \chi_{1_0} = 0.318 W$ ·· Ps = 2 \*0.318 = 0.637 ~ ... The power Conversion efficiency of is $2 = \frac{T_{L}}{P_{S}} \times 100 = \frac{0.5}{0.627} \times 100 = 78.50$ (c) - To reduce The Zero- crossium distortion in class B Power Amp. by using a high-gain op-Ame. and overall negative feedback as shown The tort dead band is reduced to tort/A. Nort. where As is The Deckain of op-Amt. - OR by biasing The complemention Transisters V. giving rise To abias current Ice. Thus for small VI, both Transistors Gudutt and crossover distortion is almost compteted a eliminated. an shown in Fig. (class AB ofp stage)

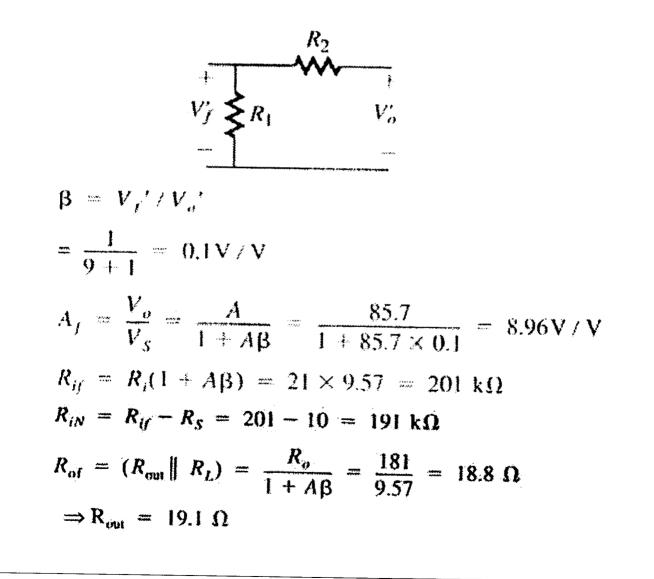

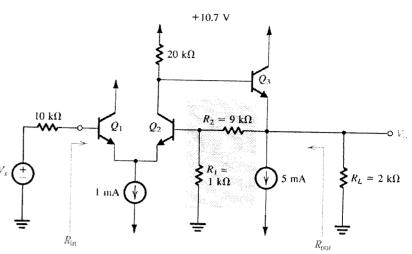

Q5: The circuit shown in Fig.() consists of a differential stage followed by an emitter follower,

with series-shunt feedback supplied by the resistors R<sub>1</sub> and R<sub>2</sub>. Assuming that the dc

K<sub>2</sub>. Assuming that the dc component of  $V_s$  is zero, and that  $\beta$  of the BJTs is very high, find:

- a) The dc operating current of each of the three transistors and show that the dc voltage at the output is approximately zero.

- b) The open loop gain (A).

- c) The feedback gain (B).

- d) The input resistance  $R_{in}$ , and The output resistance  $R_{out}$ . Assume that the transistors have  $\beta = 100$ .

## Solution:

$$I_{E1} = I_{E2} = 0.5 \text{mA}$$

$$V_{C2} = 10.7 - 0.5 \times 20 = +0.7\nu$$

$$V_o = 0.7 - V_{BE3} = 0$$

$$I_{E3} = 5 \text{mA}$$

$$r_{e1} = r_{e2} = V_A / 1 = 50\Omega, r_{e3} = 5\Omega$$

A-Circuit:

(8)

$$A = \frac{V_0}{V_1} = \frac{[20 \parallel (\beta_2 + 1)(r_{e3} + 2 \parallel 10)]}{r_{e1} + r_{e2} + \frac{10}{\beta_1 + 1} + \frac{(1 \parallel 9)}{\beta_2 + 1}} \times \frac{(2 \parallel 10)}{r_{e3} + (2 \parallel 10)} = 85.7 \text{ V/V}$$

$$R_i = R_s + (\beta + 1)(r_{e1} + r_{e2}) + R_E \parallel R_4$$

$$= 10 + 101(50 + 50) + (1 \parallel 9) = 21 \text{ k}\Omega$$

$$R_0 = 2 \parallel 10 \parallel \left[ r_{e3} + \frac{20}{\beta_2 + 1} \right] = 181 \Omega$$

**B-Circuit:**